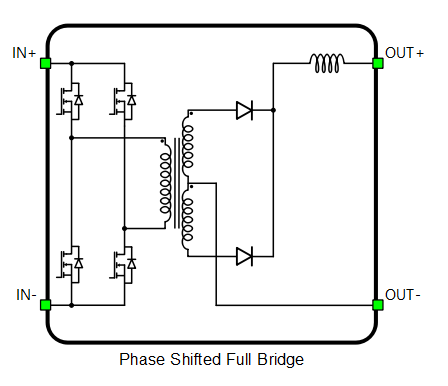

Phase Shifted Full Bridge Converter

Description of the Phase Shifted Full Bridge component in Schematic Editor

Schematic Block Diagram

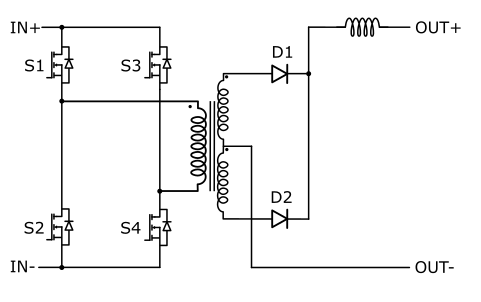

A schematic block diagram of the inverter switching block is given in Figure 2 with corresponding switch arrangement and naming.

Weight of a Phase Shifted Full Bridge converter component for real-time/VHIL simulation is 3.

For real-time/VHIL simulations, this converter requires a device configuration that supports Switch-level GDS oversampling.

Control

Selecting Digital inputs as the Control parameter enables assigning gate drive inputs to any of the digital input pins (from 1 to 32(64)). For example, if S1 is assigned to 1, the digital input pin 1 will be routed to the S1 switch gate drive. In addition, the gate_logic parameter selects either active high (High-level input voltage VIH turns on the switch), or active low (Low-level input voltage VIL turns on the switch) gate drive logic, depending on the design of the external controller. In TyphoonSim, digital signals are read from the internal virtual IO bus. Hence, if some signal is sent to digital ouput 1, it will appear on digital input 1.

Selecting Internal modulator as the Control parameter enables use of the internal PWM modulator for driving S1, S2, S3, and S4 switches instead of the digital input pins. In this configuration, three additional component inputs will be present. En input is used to enable/disable the internal PWM modulator, while InA and InB are used as reference signal inputs. When options for variable frequency or phase are selected, additional component inputs are created: Freq, OffsetA, and OffsetB respectively.

Selecting Model as the Control parameter enables setting the IGBTs' gate drive signals directly from the signal processing model. The input pin gates appears on the component and requires a vector input of four gate drive signals in the following order: [S1, S2, S3, S4]. When controlled from the model, logic is always active high.

Digital Alias

If a converter is controlled by digital inputs, an alias for every digital input used by the converter will be created. Digital input aliases will be available under the Digital inputs list alongside existing Digital input signals. The alias will be shown as Converter_name.Switch_name, where Converter_name is name of the converter component and Switch_name is name of the controllable switch in the converter.

Ports

- IN+ (electrical)

- IN side + port.

- IN- (electrical)

- IN side - port.

- OUT+ (electrical)

- OUT side + port.

- OUT- (electrical)

- OUT side - port.

- s_ctrl (in)

- Available if Model control is selected

- Vector of 4 input gate signals for switches

- En (in)

- Available if Internal modulator control is selected

- Used to enable/disable the internal modulator

- InA (in)

- Available if Internal modulator control is selected

- Used to specify modulation signal value for internal modulator phase A, switches S1 and S2

- InB (in)

- Available if Internal modulator control is selected

- Used to specify modulation signal value for internal modulator phase B, switches S3 and S4

- Freq (in)

- Available if Internal modulator control is selected and Variable carrier frequency is selected as the modulator's operation mode

- Used to specify modulator's carrier frequency

- OffsetA (in)

- Available if Internal modulator control is selected and Variable carrier phase offset is selected as the modulator's phase operation mode

- Used to specify phase A modulator's carrier phase offset

- OffsetB (in)

- Available if Internal modulator control is selected and Variable carrier phase offset is selected as the modulator's phase operation mode

- Used to specify phase B modulator's carrier phase offset

General (Tab)

- Control

- Specifies how switches are controlled. Available options are: Digital inputs, Internal modulator, and Model

- More details about each type of control can be found in the Control section

- If Digital inputs is selected as Control, the following

properties can be used:

- S1

- Digital input that is used to control the S1 switch

- S1_logic

- Logic that will be applied to control the signal for S1

- Active high or active low

- S2

- Digital input that is used to control the S2 switch

- S2_logic

- Logic that will be applied to control the signal for S2

- Active high or active low

- S3

- Digital input that is used to control the S3 switch

- S3_logic

- Logic that will be applied to control the signal for S3

- Active high or active low

- S4

- Digital input that is used to control the S4 switch

- S4_logic

- Logic that will be applied to control the signal for S4

- Active high or active low

- Gate control enabling

- If enabled, gives a possibility to control if changes in the gate control signal are applied or not

- Sen

- Available if Gate control enabling is enabled

- Digital input that enables/disables switching

- Sen_logic

- Available if Gate control enabling is enabled

- Logic that will be applied to Sen signal

- S1

- If Model is selected as Control,

the following properties can be used:

- Execution rate

- Defines the period between two updates of gate signals for the component. Gate signals are provided as a signal processing input to component.

- Execution rate

- If Internal modulator is selected as Control, the following

properties can be used:

- Operation mode

- Specifies the source of the internal modulator carrier frequency

- If Operation mode is Fixed carrier frequency, then the frequency can be specified in the component properties

- If Operation mode is Variable carrier frequency, then the frequency can be specified using a signal processing port that appears on the component.

- Carrier frequency (Hz)

- Available if the Operation mode is Fixed carrier frequency

- Specifies the internal modulator's carrier frequency

- Phase operation mode

- Specifies the source of the internal modulator carrier offset

- If Phase operation mode is Fixed carrier phase offset, then the offset can be specified in the component properties

- If Phase operation mode is Variable carrier phase offset, then the offset can be specified using a signal processing port that appears on the component

- Carrier phase offset

- Specifies the internal modulator's carrier phase offset in degrees.

- Vector containing two values: phase offset of phase A, followed by phase offset of phase B.

- Dead time period

- Specifies dead time period for the internal modulator in seconds

- Reference signal [min, max]

- Specifies carrier signal minimal and maximal value

- Vector containing two values: the minimal carrier signal value, followed by the maximal carrier signal value

- Load mode

- Specifies on which event the new value of the modulation signal will be applied

in the internal modulator

- If on min is selected, the new value will be applied when carrier reaches minimal value

- If on max is selected, the new value will be applied when carrier reaches maximal value

- If on either is selected, the new value will be applied when carrier reaches minimal or maximal value

- Specifies on which event the new value of the modulation signal will be applied

in the internal modulator

- Execution rate

- Defines the period between two updates of gate signals for the component. Gate signals are provided as a signal processing input to component

- Operation mode

Electrical (Tab)

- n1

- Specifies number of turns of the primary winding

- n2

- Specifies number of turns of the secondary winding

- L1

- Specifies leakage inductance of the primary winding

- R1

- Specifies the primary winding resistance

- L2

- Specifies leakage inductance of the secondary winding(s)

- R2

- Specifies the secondary winding resistance(s)

- Lm

- Specifies magnetization inductance

- Rm

- Specifies equivalent resistance representing the iron core losses

- Lout

- Specifies output inductor inductance

Extras (Tab)

- Public - Components marked as public expose their signals on all levels.

- Protected - Components marked as protected will hide their signals to components outside of their first locked parent component.

- Inherit - Components marked as inherit will take the nearest parent 'signal_access' property value that is set to a value other than inherit.