Linear passive components

Description of linear passive components in Schematic Editor

The Passive Components sub-folder of the Schematic Editor core library includes a variety of passive components, including:

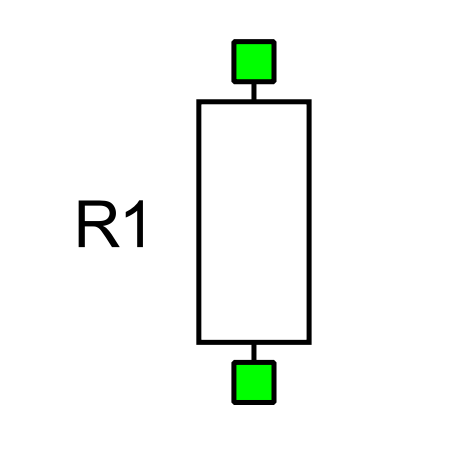

Resistor

Ports

- p_node

- Resistor p node

- n_node

- Resistor n node

Properties

- Resistance

- Value of the resistor resistance [Ω]

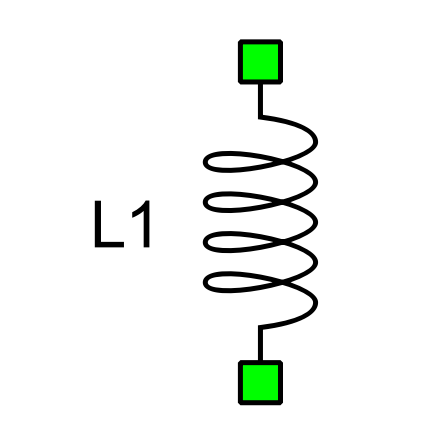

Inductor

Ports

- p_node

- Inductor p node

- n_node

- Inductor n node

Properties

- Inductance

- Value of the inductor inductance [H]

-

Initial current

- Value of the inductor initial current [A]

Extras (Tab)

The Extras tab gives you the opportunity to set Signal Access Management for the component.

Signal visibility is calculated based on the 'signal_access' property and whether or not

a parent component in its hierarchy is locked or not. Components that are not contained

within locked components expose their signals regardless of the 'signal_access'

property. The 'signal_access' property can have one of three values:

- Public - Components marked as public expose their signals on all levels.

- Protected - Components marked as protected will hide their signals to components outside of their first locked parent component.

- Inherit - Components marked as inherit will take the nearest parent 'signal_access' property value that is set to a value other than inherit.

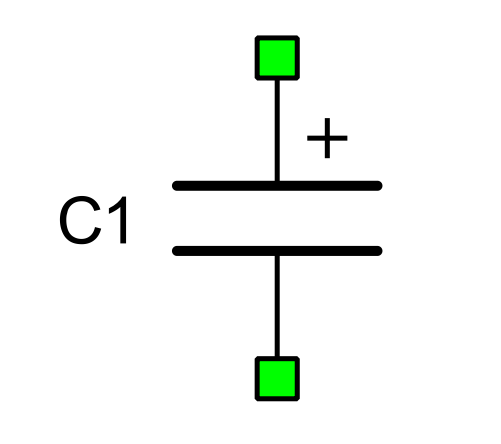

Capacitor

Ports

- p_node

- Capacitor p node

- n_node

- Capacitor n node

Properties

- Capacitance

- Value of the capacitor capacitance [F]

-

Initial voltage

- Value of the capacitor initial voltage [V]

Extras (Tab)

The Extras tab gives you the opportunity to set Signal Access Management for the component.

Signal visibility is calculated based on the 'signal_access' property and whether or not

a parent component in its hierarchy is locked or not. Components that are not contained

within locked components expose their signals regardless of the 'signal_access'

property. The 'signal_access' property can have one of three values:

- Public - Components marked as public expose their signals on all levels.

- Protected - Components marked as protected will hide their signals to components outside of their first locked parent component.

- Inherit - Components marked as inherit will take the nearest parent 'signal_access' property value that is set to a value other than inherit.

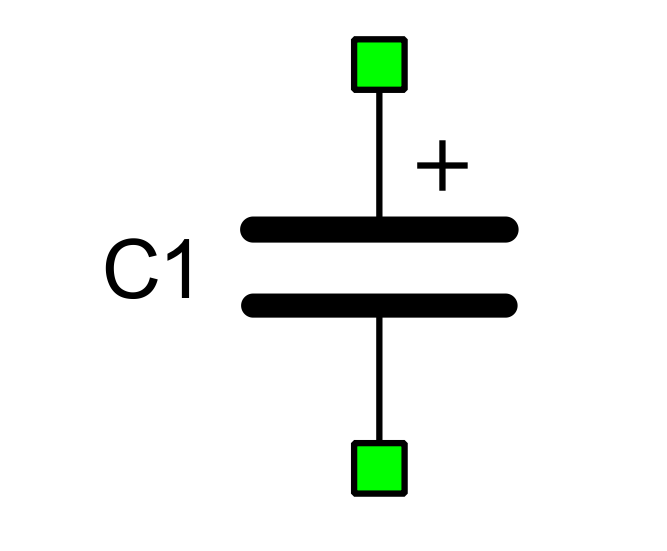

Super Capacitor

Ports

- p_node

- Super capacitor p node

- n_node

- Super capacitor n node

Properties

- Capacitance

- Value of the capacitor capacitance [F]

-

Initial voltage

- Value of the capacitor initial voltage [V]

-

Parasitics type

- Type of parasitic impedence

- Available types are None, R, and RL

-

Parasitic resistance

- Available if Parasitics type is set to R or RL

- Value of the super capacitor parasitic resistance [Ω]

-

Parasitic inductance

- Available if Parasitics type is set to RL

- Value of the super capacitor parasitic inductance [H]

Extras (Tab)

The Extras tab gives you the opportunity to set Signal Access Management for the component.

Signal visibility is calculated based on the 'signal_access' property and whether or not

a parent component in its hierarchy is locked or not. Components that are not contained

within locked components expose their signals regardless of the 'signal_access'

property. The 'signal_access' property can have one of three values:

- Public - Components marked as public expose their signals on all levels.

- Protected - Components marked as protected will hide their signals to components outside of their first locked parent component.

- Inherit - Components marked as inherit will take the nearest parent 'signal_access' property value that is set to a value other than inherit.