Detailed description

Detailed description of the HIL Nucleo-64 Interface board

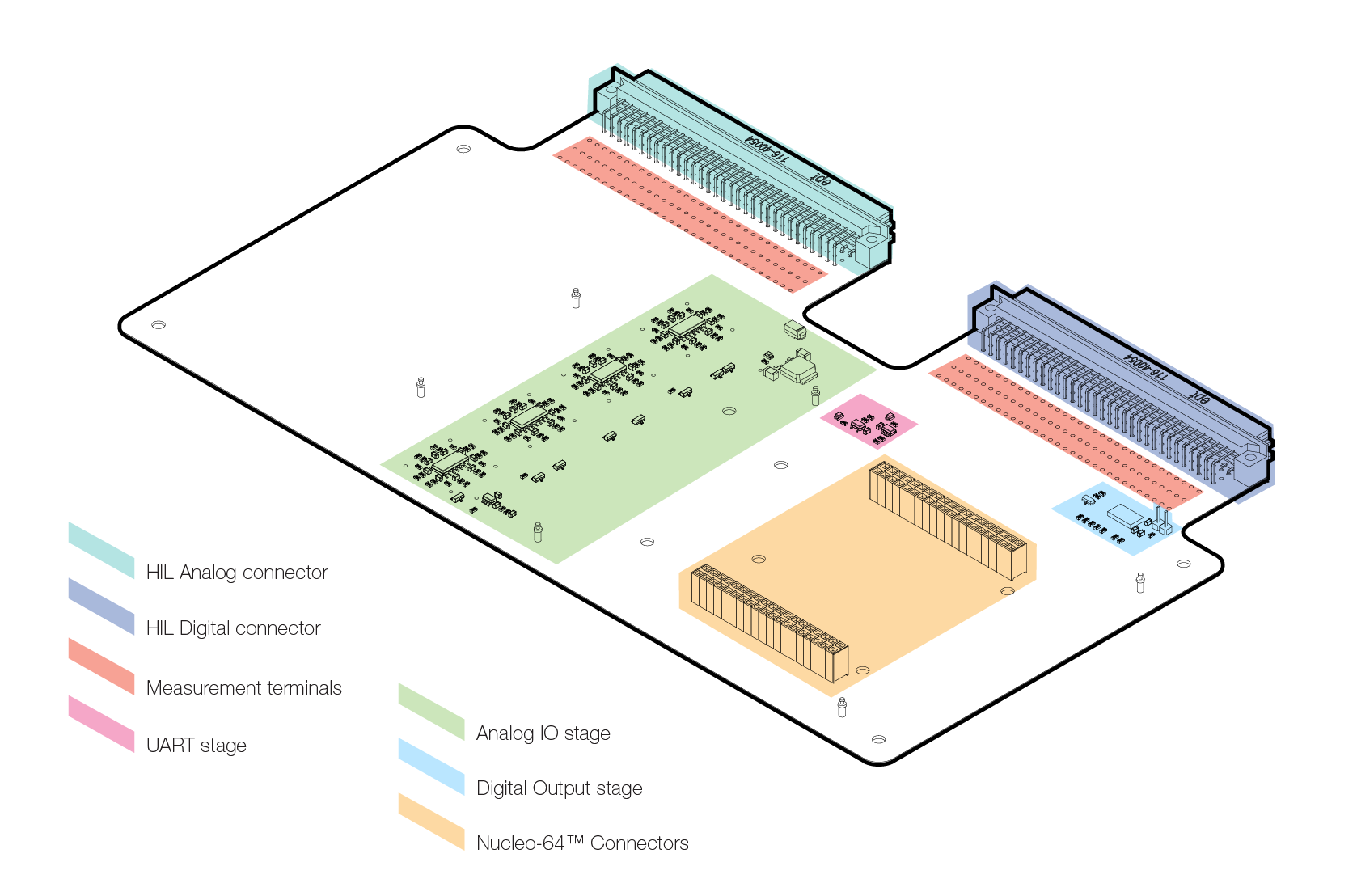

The board features the following key sections, as shown in Figure 1.

- HIL Analog connector

- HIL Digital connector

- Measurement terminals

- Analog IO stage

- Digital Output stage

- UART stage

- Nucleo-64™ Connectors

HIL Analog Connector

The HIL Analog connector is a 96 pin DIN 41612/IEC receptacle connector that is directly pluggable into the Analog I/O connector, found on all Typhoon HIL simulator devices, followed by three rows of measurement terminals. Table 1 shows how HIL analog outputs and analog inputs are connected to Nucleo-64™ sockets, for STM32F334 and STM32G474.

| HIL Analog IO | Option | STM32F334 | STM32G474 |

|---|---|---|---|

| AO1 | PC0 | ADC12_IN6 | ADC12_IN6 |

| AO2 | PC3 | ADC12_IN9 | ADC12_IN9 |

| AO3 | PC2 | ADC12_IN8 | ADC12_IN8 |

| AO4 | PC1 | ADC12_IN7 | ADC12_IN7 |

| AO5 | PA1 | ADC1_IN2 | ADC1_IN2 |

| AO6 / AI3 | PA4 | ADC2_IN1 / DAC1_OUT1 | ADC2_IN17 / DAC1_OUT1 |

| AO7 | PB0 | ADC1_IN11 | ADC1_IN15, ADC3_IN12 |

| AO8 | PA0 | ADC1_IN1 | ADC12_IN1, COMP1 |

| AO9 | PB2 | ADC2_IN12 | ADC2_IN12 |

| AO10 | PB1 | ADC1_IN12 | ADC1_IN12, ADC3_IN1 |

| AO11 | PC4 | ADC2_IN5 | ADC2_IN5 |

| AO12 | PB11 | ADC1_IN12 | ADC1_IN14 |

| AO13 / AI2 / DI7 | PA5 | ADC2_IN2 / DAC1_OUT2 | ADC2_IN13 / DAC1_OUT2 |

| AO14 / AI1 / DO4 | PA6 | ADC2_IN3 / DAC2_OUT1 | ADC2_IN3 / DAC2_OUT1 |

| AO15 / DI8 | PA7 | ADC2_IN4 | ADC2_IN4 |

| AO16 | PC5 | ADC2_IN11 | ADC2_IN11 |

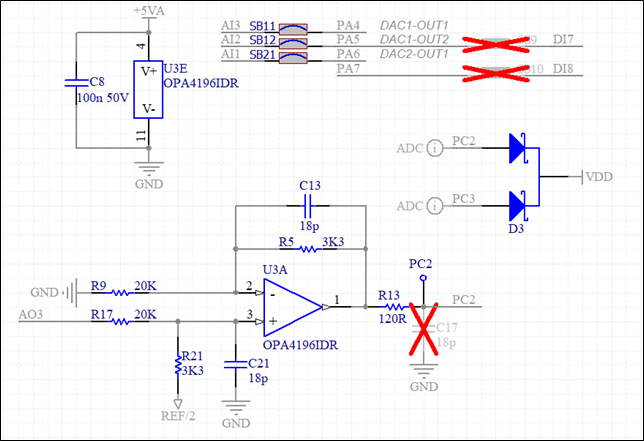

HIL Analog Outputs are scaled from +/-10 V to 0-3.3 V as shown in Figure 2. Reference voltage REF/2 is derived as one half of the voltage present on Nucleo-64™ connector CN10 pin 7 (VREF+). VREF+ can have various values depending on the inserted Nucleo-64™ board (1.8V, 2.5V, 3.25V, and 3.3V). In most cases VREF+ is 3.3V (Nucleo-64™ VDD) producing a REF/2 voltage equal to 1.65 V. The equation for scaling HIL AO output voltage to ADC input voltage is:

HIL AI1, AI2, and AI3 are connected by default (with 0R0 solder bridges SB11, SB12, and SB21) to Nucleo-64™ pins PA4, PA5, and PA6. Solder bridges SB9 and SB10 are not mounted by default.

To protect against overvoltage conditions, HIL Analog Outputs feature series 120 Ω series resistors that, together with protection diodes, form a 3.3 V clamping circuit.

HIL Digital Connector

The HIL Digital Connector is a 96 pin DIN 41612/IEC receptacle connector that is directly pluggable into the Digital I/O connector, found on all Typhoon HIL simulator devices, followed by three rows of measurement terminals. Table 2 shows how HIL digital outputs and digital inputs are connected to Nucleo-64™ sockets, for STM32F334 and STM32G474.

| HIL Digital IO | Option | STM32F334 | STM32G474 |

|---|---|---|---|

| DI7 / AO13 / AI2 | PA5 | - | - |

| DI8 / AO15 | PA7 | - | - |

| DI9 | PC8 | - | TIM8_CH3, HRTIM1_CHE1 |

| DI10 | PC9 | - | TIM8_CH4, HRTIM1_CHE2 |

| DI11 | PC6 | - | TIM8_CH1, HRTIM1_CHF1 |

| DI12 | PB9 | - | TIM8_CH3, TIM1_CH3N |

| DI13 | PA11 | TIM1_CH1N | TIM1_CH1N, HRTIM1_CHB2 |

| DI14 | PB12 | - | HRTIM1_CHC1, TIM8_CH3N, TIM1_CH3N |

| DI15 | PC7 | - | TIM8_CH2, HRTIM1_CHF2 |

| DI16 | PA9 | TIM1_CH2 | TIM1_CH2, HRTIM1_CHA2 |

| DI17 | PA8 | TIM1_CH1 | TIM1_CH1, HRTIM1_CHA1 |

| DI18 | PB15 | TIM1_CH3N | TIM1_CH3N, HRTIM1_CHD2 |

| DI19 | PB14 | TIM1_CH2N | TIM1_CH2N, HRTIM1_CHD1 |

| DI20 | PB13 | TIM1_CH1N | TIM1_CH1N, HRTIM1_CHC2 |

| DI21 | PB5 | - | TIM8_CH3N |

| DI22 | PA10 | TIM1_CH3 | TIM1_CH3, HRTIM1_CHB1 |

| DI23 | PC11 | - | TIM8_CH2N |

| DI24 | PC13 | USER BUTTON | USER BUTTON |

| DO1 | PB8 | - | HRTIM1_EEV8 |

| DO2 | PA12 | TIM1_ETR | TIM1_ETR, HRTIM1_FLT1 |

| DO3 / AO14 / AI1 | PA6 | - | - |

| DO4 | PB6 | - | TIM8_BKIN2, HRTIM1_EEV4, TIM8_ETR |

| DO5 | PB10 | TIM1_BKIN | TIM1_BKIN, HRTIM1_FLT3 |

| DO6 | PC10 | - | HRTIM1_FLT6 |

| DO7 | PC12 | - | HRTIM1_EEV1 |

| DO8 | PD2 | - | TIM8_BKIN |

| DO9 | RESET | CN7, pin 14 | CN7, pin 14 |

| DI32 | UART-TX | CN10, pin 36 (N.C.) | CN10, pin 36 (N.C.) |

| DO32 | UART-RX | CN10, pin 38 (N.C.) | CN10, pin 38 (N.C.) |

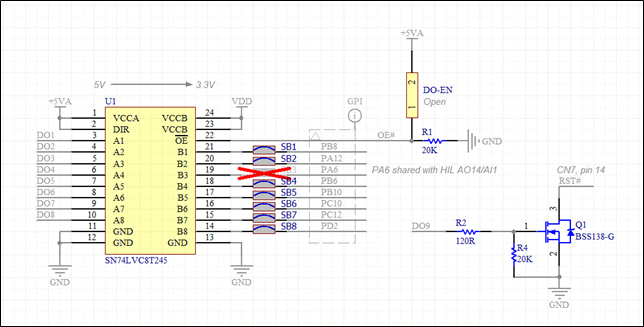

HIL Digital outputs DO1-DO8 are scaled from 5 V to 3.3 V (VDD) as shown in Figure 3. Level shifter is enabled by default (DO-EN jumper header in Open position). Inserting a jumper socket into the DO-EN jumper header will disable all outputs of the level shifter. Each level shifter output can be disconnected by removing the corresponding SB1-SB8 0R0 solder bridge. Solder bridge SB3 0R0 is not mounted by default.

DO9 is inverted into an Open-Drain and a logic high on DO9 will hold the Nucleo-64™ MCU in reset.

DO32 and DI32 (HIL DIO functioning as UART RX and TX) logic level is 3.3V.

Nucleo-64™ connectors

Pinouts for Nucleo-64™ sockets are shown in Table 3 and Table 4. Nucleo-144™ boards can also be used with limited IO count functionality.

| STM32G4xx | STM32F3xx | HIL IO | CN7 connector pins | HIL IO | STM32F334 | STM32G474 | |||

|---|---|---|---|---|---|---|---|---|---|

| HRTIM1_FLT6 | - | DO6 | PC10 | 1 | 2 | PC11 | DI23 | - | TIM8_CH2N |

| HRTIM1_EEV1 | - | DO7 | PC12 | 3 | 4 | PD2 | DO8 | - | TIM8_BKIN |

| - | - | - | VDD | 5 | 6 | E5V | - | - | - |

| - | - | - | BOOT0 | 7 | 8 | GND | GND | - | - |

| - | - | - | N.C. | 9 | 10 | N.C. | - | - | - |

| - | - | - | N.C. | 11 | 12 | IOREF | - | - | - |

| - | - | - | PA13 | 13 | 14 | RESET | DO9 | RESET | RESET |

| - | - | - | PA14 | 15 | 16 | +3.3V | - | - | - |

| - | - | - | PA15 | 17 | 18 | +5V | - | - | - |

| - | - | GND | GND | 19 | 20 | GND | GND | - | - |

| - | - | - | PB7 | 21 | 22 | GND | GND | - | - |

| USER BUTTON | USER BUTTON | DI24 | PC13 | 23 | 24 | VIN | +12V | JP5 in E5V position | JP5 in E5V position |

| - | - | - | PC14 | 25 | 26 | N.C. | - | - | - |

| - | - | - | PC15 | 27 | 28 | PA0 | AO8 | ADC1_IN1 | ADC12_IN1, COMP1 |

| - | - | - | PF0 | 29 | 30 | PA1 | AO5 | ADC1_IN2 | ADC12_IN2 |

| - | - | - | PF1 | 31 | 32 | PA4 | AO6 / AIN3 | ADC2_IN1 / DAC1_OUT1 | ADC2_IN17 / DAC1_OUT1 |

| - | - | - | VBAT | 33 | 34 | PB0 | AO7 | ADC1_IN11 | ADC1_IN15 |

| ADC12_IN8 | ADC12_IN8 | AO3 | PC2 | 35 | 36 | PC1 | AO4 | ADC12_IN7 | ADC12_IN7 |

| ADC12_IN9 | ADC12_IN9 | AO2 | PC3 | 37 | 38 | PC0 | AO1 | ADC12_IN6 | ADC12_IN6 |

| STM32G4xx | STM32F3xx | HIL IO | CN10 connector pins | HIL IO | STM32F334 | STM32G474 | |||

|---|---|---|---|---|---|---|---|---|---|

| HRTIM1_CHE2, TIM8_CH4 | - | DI10 | PC9 | 1 | 2 | PC8 | DI9 | - | TIM8_CH3, HRTIM1_CHE1 |

| HRTIM1_EEV8 | - | DO1 | PB8 | 3 | 4 | PC6 | DO11 | - | TIM8_CH1, HRTIM1_CHF1 |

| TIM8_CH3, TIM1_CH3N | - | DI12 | PB9 | 5 | 6 | PC5 | AO16 | ADC2_IN11 | ADC2_IN11 |

| - | - | VREF+ | VREF+ | 7 | 8 | U5V | - | JP5 default position | JP5 default position |

| - | - | GND | GND | 9 | 10 | N.C. | - | - | - |

| ADC2_IN13, DAC1_OUT2 | ADC2_IN2 | AO13 / AI2 / DI7 | PA5 | 11 | 12 | PA12 | DO2 | TIM1_ETR | TIM1_ETR, HRTIM1_FLT1 |

| ADC2_IN3, DAC2_OUT1 | ADC2_IN3 | AO14 / AI1 / DO3 | PA6 | 13 | 14 | PA11 | DI13 | TIM1_CH1N | HRTIM1_CHB2, TIM1_CH1N |

| ADC2_IN4 | ADC2_IN4 | AO15 / DI8 | PA7 | 15 | 16 | PB12 | DI14 | - | HRTIM1_CHC1, TIM8_CH3N |

| HRTIM1_EEV4, TIM8_ETR | - | DO4 | PB6 | 17 | 18 | PB11 | AO12 | VCAP1 (1.2V) | ADC12_IN14 |

| TIM8_CH2, HRTIM1_CHF2 | - | DI15 | PC7 | 19 | 20 | GND | GND | - | - |

| TIM1_CH2, HRTIM1_CHA2 | TIM1_CH2 | DI16 | PA9 | 21 | 22 | PB2 | AO9 | ADC2_IN12 | ADC2_IN12 |

| TIM1_CH1, HRTIM1_CHA1 | TIM1_CH1 | DI17 | PA8 | 23 | 24 | PB1 | AO10 | ADC1_IN12 | ADC1_IN12, ADC3_IN1 |

| TIM1_BKIN, HRTIM1_FLT3 | TIM1_BKIN | DO5 | PB10 | 25 | 26 | PB15 | DI18 | TIM1_CH3N | TIM1_CH3N, HRTIM1_CHD2 |

| - | - | - | PB4 | 27 | 28 | PB14 | DI19 | TIM1_CH2N | TIM1_CH2N, HRTIM1_CHD1 |

| TIM8_CH3N | - | DI21 | PB5 | 29 | 30 | PB13 | DI20 | TIM1_CH1N | TIM1_CH1N, HRTIM1_CHC2 |

| - | - | - | PB3 | 31 | 32 | GND | GND | - | - |

| TIM1_CH3, HRTIM1_CHB1 | TIM1_CH3 | DI22 | PA10 | 33 | 34 | PC4 | AO11 | ADC2_IN5 | ADC2_IN5 |

| - | - | - | PA2 | 35 | 36 | N.C. | DI32 | - | - |

| - | - | - | PA3 | 37 | 38 | N.C. | DO32 | - | - |

"Nucleo-64TM", "Nucleo-144TM", "STM32", and "STM32 Nucleo" are registered trademarks of STMicroelectronics International NV or its affiliates in the USA (US Patent and Trademark Office) and/or other countries.